# Lecture Notes in Computer Science

4236

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Luca Breveglieri Israel Koren David Naccache Jean-Pierre Seifert (Eds.)

# Fault Diagnosis and Tolerance in Cryptography

Third International Workshop, FDTC 2006 Yokohama, Japan, October 10, 2006 Proceedings

#### Volume Editors

Luca Breveglieri

Politecnico di Milano, Dipartimento di Elettronica e Informazione

Piazza Leonardo Da Vinci n. 32, 20133 Milano, Italy

E-mail: luca.breveglieri@polimi.it

Israel Koren

University of Massachusetts, Department of Electrical and Computer Engineering

Amherst, MA 01003, USA E-mail: koren@ecs.umass.edu

David Naccache

École normale supérieure, Département d'Informatique 45 rue d'Ulm, 75230 Paris Cedex 05, France

E-mail: david.naccache@ens.fr

Jean-Pierre Seifert

University of Haifa, Faculty of Science and Science Education The Center for Computational Mathematics and Scientific Computation 31905 Haifa, Israel

E-mail: jeanpierreseifert@yahoo.com

Library of Congress Control Number: 2006933937

CR Subject Classification (1998): C.2.0, D.4.6, E.3, H.2.0, K.4.4, K.6.5

LNCS Sublibrary: SL 4 – Security and Cryptology

ISSN 0302-9743

ISBN-10 3-540-46250-3 Springer Berlin Heidelberg New York ISBN-13 978-3-540-46250-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11889700 06/3142 5 4 3 2 1 0

#### **Preface**

In recent years applied cryptography has developed considerably to satisfy the increasing security requirements of various information technology disciplines, such as telecommunications, networking, database systems, mobile applications and others. Cryptosystems are inherently computationally complex and in order to satisfy the high throughput requirements of many applications, they are often implemented by means of either VLSI devices (cryptographic accelerators) or highly optimized software routines (cryptographic libraries) and are used via suitable (network) protocols.

The sophistication of the underlying cryptographic algorithms, the high complexity of the implementations, and the easy access and low cost of cryptographic devices resulted in increased concerns regarding the reliability and security of crypto-devices. The effectiveness of side channel attacks on cryptographic devices, like timing and power-based attacks, has been known for some time. Several recent investigations have demonstrated the need to develop methodologies and techniques for designing robust cryptographic systems (both hardware and software) to protect them against both accidental faults and maliciously injected faults with the purpose of extracting the secret key. This trend has been particularly motivated by the fact that the equipment needed to carry out a successful side channel attack based on fault injection is easily accessible at a relatively low cost (for example, laser beam technology), and that the skills needed to use it are quite common. The identification of side channel attacks based on fault injections and the development of appropriate counter-measures have therefore become an active field of scientific and industrial research.

Following this trend, the first workshop devoted to Fault Diagnosis and Tolerance in Cryptography (FDTC) was organized in June 2004, in Florence, Italy, to promote the exchange of ideas within the community of researchers who have been active in this field. The workshop has since then become an annual event with the second one held in Edinburgh, Scotland, in September 2005, and the third one in Yokohama, Japan, in October 2006. FDTC 2006 included 12 regular presentations plus two invited talks that provided an overview of the state of the art in this field.

The FDTC workshops aim at covering all aspects of fault injection-based side channel attacks on cryptographic devices and the corresponding counter-measures. This includes topics such as: modelling the reliability of cryptographic systems and protocols; inherently reliable cryptographic systems and algorithms; fault models for cryptographic devices (hardware and software); fault-injection-based attacks on cryptographic systems and protocols; adapting classical fault diagnosis and tolerance techniques to cryptographic systems; novel fault diagnosis and tolerance techniques for cryptographic systems; case studies of attacks, reliability and fault diagnosis and tolerance techniques in cryptographic systems.

FDTC 2006 has for the first time official proceedings as a Springer LNCS volume. The present volume contains all the papers presented at FDTC 2006, plus selected FDTC 2004 and 2005 papers that have undergone a second review process, which have been co-chaired for this Springer volume by David Naccache and Jean-Pierre

Seifert. The main goal of this volume is to provide the reader with a comprehensive introduction to the issues faced by designers of robust cryptographic devices and to the currently available methodologies and techniques for protecting these devices against fault injection attacks.

The papers contained in this volume are organized as follows. Section 1 includes new fault-injection-based attacks on public key systems, namely, RSA and ECC. Section 2 contains several proposed counter-measures, mainly at the algorithmic level, that are based on the use of fault diagnosis methods. Section 3 is dedicated to fault injection-based attacks on symmetric key systems and the related fault-diagnosis counter-measures. Section 4 focuses on models for evaluating the reliability and security of cryptographic systems that are subject to fault injection-based attacks. Section 5 is dedicated to counter-measures at the arithmetic level, which complement those at the algorithmic level mentioned above. Section 6 contains a miscellanea of topics demonstrating the connection between fault injection-based attacks and other security side channel threats, e.g., power attacks.

The interested reader may also wish to read the papers that have appeared in the "Special Section on Fault Diagnosis and Tolerance in Cryptography" of the September 2006 issue of the *IEEE Transactions on Computers*. This special section includes the extended version of several FDTC 2004 presentations (and consequently do not appear in this volume). Also worth mentioning is the February 2006 *Special Issue of the Proceedings of the IEEE* which is devoted to cryptography and contains a tutorial paper focusing on fault injection-based side channel attacks that was originally presented at FDTC 2004.

This workshop would not be possible without the involvement of many people, in particular the members of the Program Committee who reviewed all the submitted manuscripts. Their names are listed below. Thanks are also due to Alfred Hofman, who accepted our proposal to publish an LNCS volume dedicated to FDTC. We also wish to thank Akashi Satoh, Natsume Matsuzaki and Tsutomu Matsumoto for their tremendous help with the local arrangements in Yokohama. Last but not least, we would like to thank all the authors who have submitted their papers and greatly contributed to the success of the FDTC workshops.

August 2006

Luca Breveglieri Israel Koren David Naccache Jean Pierre Seifert

# **Organization**

## **Organizing Committee**

Luca Breveglieri (volume contact editor)

Politecnico di Milano

Dipartimento di Elettronica e Informazione

Piazza Leonardo Da Vinci n. 32

Milan 20133

Italy

luca.breveglieri@polimi.it

Israel Koren

University of Massachusetts at Amherst

Department of Electrical and Computer Engineering

Amherst, MA 01003

USA

koren@ecs.umass.edu

David Naccache École Normale Supérieure de Paris Département d'Informatique 45 rue d'Ulm 75230 Paris Cedex 05 France david.naccache@ens.fr

Jean-Pierre Seifert Applied Security Research Group The Center for Computational Mathematics and Scientific Computation Faculty of Science and Science Education University of Haifa Haifa 31905, Israel

#### and

Institute for Computer Science University of Innsbruck 6020 Innsbruck, Austria jeanpierreseifert@yahoo.com

#### **Program Committee of FDTC 2006**

Bao FengI2R Corporation, FranceLuca BreveglieriPolitecnico di Milano, ItalyErnie BrickellIntel Corporation, USA

Hervé Chabannes Sagem Défense Sécurité, France Christophe Clavier Gemplus Corporation, France Wieland Fischer Infineon Corporation, Germany Christophe Giraud Oberthur Card Systems, France

Shay Gueron University of Haifa and Intel Corporation, Israel

Louis Goubin University of Versailles, France Mohamed Kafi Axalto Corporation, France

Ramesh Karri Polytechnic University of Brooklyn, USA

Jong Rok KimSamsung Corporation, KoreaVanessa GratzerUniversity of Paris 2, FranceÇetin Kaya KoçOregon State University, USA

Israel Koren University of Massachusetts at Amherst, USA Pierre-Yvan Liardet STMicroelectronics Corporation, France

Wenbo Mao HP Corporation, USA Sandra Marcello Thalès Corporation, France

David Naccache École Normale Supérieure de Paris, France

(PC Co-chair)

Elisabeth Oswald Graz University of Technology, Austria

Jean-Pierre Seifert University of Innsbruck, Austria and University of

Haifa, Israel (PC Co-chair)

Elena Trichina Spansion Corporation, USA

Michael Tunstall Royal Holloway University of London, UK

Wen-Guey Tzeng National Chiao Tung University, Taiwan

Claire Whelan Dublin City University, Ireland

Kaiji Wu University of Illinois at Chicago, USA

Moti Yung Columbia University, USA

#### **Program Committee of FDTC 2005**

Luca Breveglieri Politecnico di Milano, Italy

Joan Daemen STMicroelectronics Corporation, Belgium

Christophe Giraud Oberthur Card Systems, France

Shay Gueron Intel Corporation, Israel

Marc Joye Gemplus & CIM-PACA, France Mark Karpovsky University of Boston, USA Çetin Kaya Koç Oregon State University, USA

Israel Koren University of Massachusetts at Amherst, USA

Régis Leveugle TIMA Laboratory Grenoble, France Ramesh Karri Polytechnic University of Brooklyn, USA

David Naccache Gemplus Card International, France, and Royal Holloway,

UK

Christof Paar University of Ruhr at Bochum, Germany

Jean-Pierre Seifert Intel Corporation, USA

#### **Program Committee of FDTC 2004**

Luca Breveglieri Politecnico di Milano, Italy

Joan Daemen STMicroelectronics Corporation, Belgium

Çetin Kaya Koç Oregon State University, USA

Israel Koren University of Massachusetts at Amherst, USA

Régis Leveugle TIMA Laboratory Grenoble, France

David Naccache

Ramesh Karri Polytechnic University of Brooklyn, USA

Christof Paar University of Ruhr at Bochum, Germany

# **Table of Contents**

| Attacks on Public Key Systems                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Is It Wise to Publish Your Public RSA Keys? (2006)                                                                          | 1  |

| Wagner's Attack on a Secure CRT-RSA Algorithm Reconsidered                                                                  |    |

| (2006)                                                                                                                      | 13 |

| Attacking Right-to-Left Modular Exponentiation with Timely Random Faults (2006)                                             | 24 |

| Sign Change Fault Attacks on Elliptic Curve Cryptosystems                                                                   |    |

| (2004-05)                                                                                                                   | 36 |

| Cryptanalysis of Two Protocols for RSA with CRT Based on Fault Infection (2004-05)                                          | 53 |

| Protection of Public Key Systems                                                                                            |    |

| Blinded Fault Resistant Exponentiation (2006)                                                                               | 62 |

| Incorporating Error Detection in an RSA Architecture (2004-05) Luca Breveglieri, Israel Koren, Paolo Maistri, Moris Ravasio | 71 |

| Data and Computational Fault Detection Mechanism for Devices That Perform Modular Exponentiation (2004-05)                  | 80 |

| Attacks on and Protection of Symmetric                                                                                      |    |

| Key Systems                                                                                                                 |    |

| Case Study of a Fault Attack on Asynchronous DES Crypto-Processors (2006)                                                   | 88 |

| A Fault Attack Against the FOX Cipher Family (2006) Luca Breveglieri, Israel Koren, Paolo Maistri                         | 98  |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| Fault Based Collision Attacks on AES (2006)                                                                               | 106 |

| An Easily Testable and Reconfigurable Pipeline for Symmetric Block Ciphers (2006)                                         | 121 |

| Models for Fault Attacks on Cryptographic Devices                                                                         |     |

| An Adversarial Model for Fault Analysis Against Low-Cost<br>Cryptographic Devices (2004-05)                               | 131 |

| Cryptographic Key Reliable Lifetimes: Bounding the Risk of Key Exposure in the Presence of Faults (2004-05)               | 144 |

| A Comparative Cost/Security Analysis of Fault Attack Countermeasures (2004-05)                                            | 159 |

| Fault-Resistant Arithmetic for Cryptography                                                                               |     |

| Non-linear Residue Codes for Robust Public-Key Arithmetic (2006)                                                          | 173 |

| Fault Attack Resistant Cryptographic Hardware with Uniform Error Detection (2004-05)                                      | 185 |

| Robust Finite Field Arithmetic for Fault-Tolerant Public-Key Cryptography (2004-05)                                       | 196 |

| Fault Attacks and Other Security Threats                                                                                  |     |

| DPA on Faulty Cryptographic Hardware and Countermeasures (2006) Konrad J. Kulikowski, Mark G. Karpovsky, Alexander Taubin | 211 |

| Fault Analysis of DPA-Resistant Algorithms (2006) Frederic Amiel, Christophe Clavier, Michael Tunstall                    | 223 |

|                                                            | Table of Contents | XIII |

|------------------------------------------------------------|-------------------|------|

| Java Type Confusion and Fault Attacks (2006) Olli Vertanen |                   | 237  |

| Author Index                                               |                   | 253  |

# Is It Wise to Publish Your Public RSA Keys?

Shay Gueron<sup>1,3</sup> and Jean-Pierre Seifert<sup>1,2</sup>

<sup>1</sup> Applied Security Research Group

The Center for Computational Mathematics and Scientific Computation,

University of Haifa, Haifa 31905, Israel

<sup>2</sup> Institute for Computer Science, University of Innsbruck

6020 Innsbruck, Austria

<sup>3</sup> Intel Corporation, IDC, Israel

shay@math.haifa.ac.il

jeanpierreseifert@yahoo.com

**Abstract.** Only very recently, the study of introducing faults into the public-key elements of the RSA signature scheme was initiated. Following the seminal work of Seifert on fault inductions during the RSA signature verification, Brier, Chevallier-Mames, Ciet, and Clavier considered in a recent paper the signature counterpart and showed how to recover the private exponent — even with absolutely no knowledge of the faults behavior. Consequently, this paper reconsiders the RSA signature verification and proposes two embassaring simple new fault attacks against the RSA verification process. Despite their trivial nature, both of our methods bear heavy practical consequences. While the first new attack of our methods simply eliminates the "somehow cumbersome" and subtle mathematical two-phase attack analysis of Seifert's attack, the second methodology removes the so called "one-shot success" of Seifert's attack and paves the way for a permanent and universal "mass-market" RSA signature forgery. Motivated by the obvious security threats through tampering attacks during the RSA verification process we will also consider some heuristic but practical countermeasures.

**Keywords:** Authenticated computing, Fault attacks, Hardware attacks, RSA, Secure/Trusted boot.

#### 1 Introduction

In the context of tamper-resistant devices that implement the RSA algorithm, most of the concern and the efforts for countermeasures against "physical attacks" are directed towards protecting the signature procedures. These are perceived sensitive because they involve operations that use the device's secret exponent. The general perception here is that the RSA verification process is inherently secure because it only deals with public information.

But, continuing the recently introduced fault attacks against the public keys of an RSA system, cf. [Sei, Mui, BCCC], this paper casts new doubts on the above perception. We show that if the threat model includes tampering with the

L. Breveglieri et al. (Eds.): FDTC 2006, LNCS 4236, pp. 1–12, 2006.

device, fault attacks become a real practical threat to the trustworthiness of the authentication procedure.

To put a real practical perspective on the former attack scenario, consider a device which is a locked system that is supposed to execute some input code, but only this code is signed and the signature is validated. This is a standard situation with various DRM applications. Since the user is part of the threat model in such cases, hardware attacks that include tampering with the device are a plausible concern. The big threat to the device is a so called BORE (Break Once Run Everywhere) attack, similar to those that exist in the smartcard business, where a successful attack can be reproduced and then applied to many devices. In such real-world scenarios, it is conceivable that the attacker would invest even significant initial effort in hacking the device, would manage to build a cheap hardware device that circumvents this authentication, and then publicly sell (or distribute) this circumvention device. One known example for a BORE attack is the "unlooper" business, where fraudulent pay-TV users install a cheap device in order to circumvent the pay-TV protection mechanism. The unlooper device induces the right spikes, glitches, etc. in order to "unlock" an invalid smartcard, cf. [And, BCNT<sup>+</sup>, Unl]. Another prominent example is the X-box, where despite the cryptographically strong RSA authentication procedure that it implemented, a trivial change in the public key value lead to a total security break, cf. [Hua], or [Har] for details about the commercial authentication-circumvention business.

Indeed, this paper discusses two very simple but practical types of fault based attacks against a device that performs RSA authentication, facilitating the signature forgery dramatically. Following the seminal work of Seifert [Sei] on fault inductions during the RSA signature verification, Brier, Chevallier-Mames, Ciet, and Clavier [BCCC] considered in a recent paper the signature counterpart and showed how to recover the private exponent — even with absolutely no knowledge of the faults behavior. Consequently, this paper reconsiders the RSA signature verification and proposes two embassaring simple new fault attacks aginst the RSA verification process. Despite their trivial nature, both of our methods bear heavy practical consequences. While the first new attack of our methods only eliminates the "somehow cumbersome" and subtle mathematical two-phase attack analysis of Seifert's attack, the second methodology removes the so called "one-shot success" of Seifert's attack and paves the way for a permanent and universal "mass-market" RSA signature forgery.

Our new attacks undermine again the underlying assumption upon which the authentication is based, namely that the device uses an authentic copy of the public data. Thus, the conclusion is that if a device cannot remotely verify the authenticity of the public data, and can be physically manipulated by an attacker, new types of countermeasures against faults induction, must be taken. In the context of Elliptic Curve Cryptography this fact was already known, cf. [BMM, CJ].

The present paper is organized as follows. The next section recalls some basic definitions, presents the used fault models, and as well the simple attack idea due to Seifert, cf. [Sei]. Herafter, we will show our two new very simple attack

methodologies, called bypass attack and permanent fault attack. Then, we will investigate some simple but practical countermeasures to thwart the known fault attacks against the RSA signature verification process. The paper concludes with recommendations for further research directions.

#### 2 Definitions and Preliminaries

An RSA system for bit-length k is defined as follows, see for e.g. [MvOV]. Uniformly pick from the set of all k/2-bit primes two secret primes p and q and let  $N=p\cdot q$  be their respective product. Then, uniformly pick from the set  $Z_N^*$  a number e. Here,  $\mathbb{Z}_N^*$  denotes the multiplicative group of all natural numbers which are smaller than N and are relatively prime to N. Using p and q compute now the e's multiplicative inverse d such that  $e \cdot d \equiv 1 \mod \varphi(N)$ . Finally, one announces the public key e and N and keeps the key d secretly.

In order to actually sign with RSA in the standard way, one uses a hash function  $\mathsf{hash}(\cdot)$  (for e.g. SHA-1) and a redundancy function  $\mathsf{F}(\cdot)$  in the following way, cf. [MvOV]. First, one hashes the messages  $m \in \mathbb{Z}_N$  to a fixed length hash value  $h_m := \mathsf{hash}(m)$ , hereafter one uses the redundacy function  $\mathsf{F}$  to re-expand the hash value  $h_m$  into an k-bit value  $f_m := \mathsf{F}(h_m)$ , and finally one computes the RSA-signature of the message m as  $S := (f_m)^d \mod N$  using the private exponent d and the modulus N. For clarity, we will give a detailed standard RSA signature authentication flow below in Figure 1.

```

input: m, S, N

ROM (or fuse) storage: h_N

1. /* validate N

a. t := \mathsf{hash}(N);

b. if t \neq h_N then output "fail" and stop;

2. /* validate m

a. h_m := \mathsf{hash}(m);

b. a := S^e \mod N;

c. extract the expected hash value e_m from a;

d. if h_m \neq e_m then output "fail" and stop;

"accept" message m if and only if N and m were valid

```

Fig. 1. Standard RSA signature authentication flow

A standard RSA authentication flow. The inputs includes the message m to be authenticated, the RSA public modulus N, the public exponent e, and the signature S on the hash value (denoted by  $\mathsf{hash}(m)$ ) of the authentic message m. This signature S is computed by the signer, using his private RSA exponent.

To avoid alleviate expensive ROM or fuse storage for the complete value of N, the device stores a trusted copy of its hash value  $\mathsf{hash}(N)$ . The input public modulus N is validated first, by computing its hash value and comparing it to  $\mathsf{hash}(N)$ . The validation of the message follows, and is carried out by performing the required modular exponentiation, and comparing the extracted hash to the hash value of m.

#### 2.1 The Physical Fault Model or Recalling Seifert's Attack

Without an exhaustive elaboration on the concrete realization of fault attacks or on the various existing (mathematical) models we will briefly describe our simple model of transient fault attacks when applied to a computing device under attack. For a thorough treatment of their physical realization we refer to [ABFHS, BCNT<sup>+</sup>] and for a proper mathematical treatment we refer to [BOS, LP]. As in [BDL] or many other related publications, we assume that the attacker is able to enforce random register faults, resulting in a uniformly chosen register content. The only preciseness on the induced fault is the precise timing on the register fault. Note that this is a weak assumption as the timing can be fully controlled or observed by the attacker at least in open computing devices with some equipment — which is our overall assumption. Given the strong practically demonstrated results on faults attacks, cf. [ABFHS, BCNT<sup>+</sup>], our simple model seems fairly valid.

Seifert's attack, cf. [Sei] is based on a simple idea. Induced data faults can be used in order to change the value of the public modulus. If the attacker can change N to a new fake modulus, N', that he can factor, then he can easily derive a fake private exponent d', and use it to compute a signature S' of a message m. The question that arises is, therefore, how easy is it to transform N to a precomputed value N' by means of random faults on N. This question was recently discussed in [Sei] and enhanced in [Mui], where it was shown that this is indeed easy. Given some 1024-bit RSA modulus, there is a probability of more than 50% that it could be transformed to an easy factorable fake modulus, by affecting only 4 bits, and for a 2048 bits modulus, this can be achieved by changing only 6 bits. Consequently, the attacker's strategy is the following. Using the public value of N, he goes (off-line) over all the new values that differ from N by only b least significant bits, for some small b, and finds (if possible) a derived value which is a prime number (or has otherwise an easy factorization). If manipulating only b bits does not yield a desirable fake modulus, the attacker simply increases the search space by using a larger value of b. To illustrate the above strategy, consider the following very simple example. For realistically large parameters, and small practical bound on the search space, we chose a random string T of 1012 bits, multiplied it by 2006 (standing for the current year), and constructed N = pq where p and q were defined as the two next primes exceeding  $2006 \cdot T$ . To account for tampering with at most the 10 least significant bits of N, we screened (offline) the numbers  $\hat{N} = i + N - (N \mod 512)$ , for  $i = 1, 2, \dots, 511$ . Starting from the value

$N = 1810 {\rm FAB24763BD3C20A4DA2464B68ADB36A2A39FFEECF6A5453DA269CCE5} \\ 870 {\rm F3A309C1211131977AA9D523263222BAAA19E1B2318BD37B3967FDEF5} \\ 840 {\rm 76F54543267162BFF9C9907A175271435D38EE7068D1CF020E2DC0D28} \\ 0879 {\rm 41F59B382D9EBAFACA46FD9433D9D6E2AC97BDC2C793FB744C1EB01D} \\ 840 {\rm B2F230E713431E93B4385354589DEA67C559FE6AF6550863446FA941B} \\ 62 {\rm EC6313ECC4B09A65A201FD61113DE425602DACCE8E32A2A75E2A6CD8A8} \\ 0A5 {\rm F42FCA7699AEA53D64BB43898C5E12509A72AE6AF60A9A9CC77AC7C53} \\ 9E {\rm E8BEC9A4FD587CE7ED0148FFE25AA1F2A1ABF073CE84A0E11F2EEBDE48} \\ AFCEF1EAACED6F2ACE110DEEDD5$

a prime N' was found for i = 35, namely,

$N' = 1810 \text{FAB} 24763 \text{BD} 3C20 \text{A4D} \text{A2464B68ADB} 36A2 \text{A39FFEECF6A5453DA269CCE5} \\ 870 \text{F3A309C1211131977AA9D523263222BAAA19E1B2318BD37B3967FDEF5} \\ 84D 76 \text{F54543267162BFF9C9907A175271435D38EE7068D1CF020E2DC0D28} \\ 087941 \text{F59B382D9EBAFACA46FD9433D9D6E2AC97BDC2C793FB744C1EB01D} \\ 840 \text{B2F230E713431E93B4385354589DEA67C559FE6AF6550863446FA941B} \\ 62 \text{EC6313ECC4B09A65A201FD61113DE425602DACCE8E32A2A75E2A6CD8A8} \\ 0A5 \text{F42FCA7699AEA53D64BB43898C5E12509A72AE6AF60A9A9CC77AC7C53} \\ 9E \text{E8BEC9A4FD587CE7ED0148FFE25AA1F2A1ABF073CE84A0E11F2EEBDE48} \\ \text{AFCEF1EAACED6F2ACE110DEEC23}.$

At this point the attacker can sign any message with modulus N', public exponent e and fake private exponent d' satisfying  $e \cdot d' = 1 \mod (N'-1)$ , which is trivial to compute, assuming (with high probability)  $\gcd(e,(N'-1))=1$ ). To make the device accept the message as authentic, the attacker simply induces random faults on the least significant chunk of N. He repeats this fault induction until N is converted to N'. These faults must be induced after the off-line phase and before the authentication flow, so as to pass the public key validation. Since theory indicates that a favorable fake modulus N' can be obtained by tampering with a small number of bits, the search space for the results that are obtained by the random faults is small enough to make the attack practical with a number of several such attempts.

Observe now, that verifying or creating an RSA signature on a standard CPU is due to the underlying long modular multiplication a quite complicated task. Especially, even modern high end CPUs cannot handle a full RSA modulus, say 2048 bits, in one single register (operation). Therefore a chain of successive operations is needed just when loading or preparing an RSA modulus from some memory into a set of CPU registers. Once the modulus is prepared across several CPU registers it will be used from there until the end of the full RSA operation. The long sequence of underlying squares and multiplies must frequently use the RSA modulus which is therefore permanently stored in some CPU registers.

Thus, during loading or preparing the long RSA modulus we are able — according to our above model — to draw an arbitrary but given small number of least significant bits of a RSA modulus from a uniform distribution. Simply enforce several fault attacks during several successive loads of multiple CPU registers which together represent the correct number of required bits beyond the smaller register length.

#### 3 Novel Fault Attacks Against RSA Authentication

While the formerly described Seifert attack scenario looks like indeed feasible — given its liberal transient fault induction method — we will now describe two new attack scenarios, being much more practical. Compared to the Seifert attack scenario they offer the following attacker's advantages.

- Instead of transient data errors it assumes that the attacker can change by inducing faults the control flow, which is investigated for the prominent public exponent e=5. This attack has the advantage that it eliminates the "somehow cumbersome" and subtle mathematical two-phase attack analysis of Seifert's attack.

- The second new attack assumes that the attacker is able to invest even a significant initial effort in inspecting the underlying piece of silicon upfront. I.e., we assume that he can do even a full reverse engineering of the chip under attack. This reverse engineering knowledge is then used to modify "customer devices" by simple permanent fault attacks through FIB (Focused Ion Beam), Eddy Currents or other methods, etc., cf. [FIB, QS, BCNT<sup>+</sup>]. This then enables to avoid the so called "one-shot success" of Seifert's attack and paves the way for a permanent and universal "mass-market" RSA signature forgery, without building a dedicated hardware device that circumvents the RSA authentication.

#### 3.1 Bypass Fault Attacks

While the formerly described Seifert attack against RSA verification is targeted towards the general case for a randomly chosen  $e \in \mathbb{Z}_N^*$ , in practice most often a fixed low exponent e is used. So let us consider the more practical case, as shown in the following Figure 2.

Now, consider potential so called bypass attacks, as described for e.g. in [BCNT<sup>+</sup>]. Bypass attacks are based on purposely inducing some errors by the attacker, in a way that the authentication flow is changed. There are several potential vulnerabilities arising.

- Bypass the exponentiation loop. This implies that instead of computing  $S^5 \mod N$ , the flow computes only  $S \mod N$ . Therefore, the attacker can force the device to accept any signature.

- Bypass the "N validation step". In that case, the attacker can forge N. This would allow the attacker to eventually sign any message.

```

input: m, S, N

ROM (or fuse) storage: h_N

t := \mathsf{hash}(N);

if t \neq h_N then output "fail" and stop;

h_m := \mathsf{hash}(m);

a := S;

repeat 2 times

a := a^2 \bmod N;

a := a \cdot S \bmod N;

extract the expected hash value e_m from a;

if h_m \neq e_m then output "fail" and stop;

"accept" message m if and only if N and m were valid

```

**Fig. 2.** RSA signature authentication flow for e=5

- Bypass the final "hash value check".

To accomplish one of these attacks, the attacker needs only to find one successful error to be induced in one device. Since errors are typically repeatable, finding one "bypass" error could enable the construction of a dedicated hacker device that circumvents the RSA authentication procedure in all devices of the same type. See [BCNT<sup>+</sup>] for practical implementations of such bypass attacks showing that they are relatively easy in practice.

#### 3.2 Permanent Fault Attacks

In this strong fault model, we assume that the attacker is all powerful and even able to fully reverse-engineer the whole piece of silicon under attack. Knowing completely every single transistor of the chip the following is a possible fault attack threat scenario leading to a so called permanent fault attack. The Permanent Fault Attack (PFA) is a way to circumvent the authentication mechanism by completely undermining the anchor of trust — by faking N permanently. To do this, the steps for realizing a commercial PFA are as follows.

- The attacker computes from the public N some public key at will, say N', whose factorization is known to him.

- The attacker computes  $\mathsf{hash}(N')$ .

- The attacker compares the strings  $\mathsf{hash}(N)$  and  $\mathsf{hash}(N')$ . Both values are h bits strings (e.g., h = 160 for SHA-1).

- The attacker marks the locations of the bits where  $\mathsf{hash}(N)$  and  $\mathsf{hash}(N')$  do not agree.

- Using the methods described in [FIB, QS, BCNT<sup>+</sup>], the attacker induces permanent faults on sample devices (the authentication device) until he manages to transform  $\mathsf{hash}(N)$  into  $\mathsf{hash}(N')$ .

- Once this is successfully done for one device, the attacker can start to sell his "unlocking-service" to the market which consists of:

- Taking a customer device, changing its hash(N) to hash(N').

- Giving the customer either the new private RSA exponent d' or giving him directly a new code enabling the device's new services.

- Sending the customer's device back to the customer including the private exponent d' including new code.

- The attacker sells now his comprehensive web-service to customers who can load messages that are signed by the attacker (or the customer itself) (a degenerate case would be that N' is trivial, which allows anyone to forge any message).

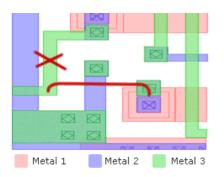

To demonstrate that permanent fault attacks are no "fiction" at all and are very simple to achieve (say with a FIB machinery), we would like to show the following picture from [FIB]. It shows the precise disconnect of a certain metal connection and its corresponding reconnect at a different place.

Fig. 3. Permanent fault attack via Focused Ion Beam

We would like to make the following comments on the above attack.

- For how to realize permanent fault attacks without opening the package, we refer especially to [QS, BCNT<sup>+</sup>] and the above Figure 3 which shows why and how (simple it is) to mount such attacks in a cheap way.

- After one device is successfully modified, "mass market productization" of PFA's can be deployed.

- Reverse-engineering and "re-wiring" a complete piece of silicon is indeed a very powerful technique, especially given the recent result that there is no hope of any mathematical "obfuscation technique", i.e., to hide mathematically a secret inside a circuit, cf. [BGIR<sup>+</sup>], assuming that the adversary is very powerful. Indeed, this cost-intensive method might be an interesting business for a "mass-market productization" of turning a cheap piece of silicon into a premium piece of silicon.

Finally, we would like to note that this permanent fault attack avoids the so called "one-shot success" of Seifert's attack and paves the way for a permanent and universal "mass-market" RSA signature forgery, without building a dedicated hardware device that circumvents the RSA authentication. Also, the "price" of this attack is directly linked with the number of bits to be changed to obtain a useful  $\mathsf{hash}(N')$ , which was recently improved by Muir [Mui].

#### 4 Mitigating Fault Attacks Against RSA Authentication

Motivated by the different threats through the formerly described various fault attack models, we will now gradually and seperately develop for each of the individual different attack scenarios a heuristic countermeasure. In addition to our disclaimer about their perfect security we also expect them in practice to be somehow combined with each other and other best known countermeasures against fault attacks.

#### 4.1 Mitigating Seifert-Like Attacks

To mitigate an RSA authentication process against Seifert-like attacks, we propose in Figure 4 the following so called *Interleaved Validation Scheme*, where an unpredictable multiple of N is computed before the modulus validation step (i.e., before N can be modified by the attacker to N'). This value is embedded into the modular exponentiation flow, and "blinds" the exponentiation base. The attacker cannot select N' in a way that the exponentiation result is still unchanged modulo N'. The additional computational cost of these countermeasures is relatively small.

Here, u is an unpredictable value that depends on the modulus N, and computed before N is validated (i.e., before it can be modified to the "attacker's selected" N'). This value is embedded into the modular exponentiation flow, which takes place during the signature validation phase. Since u is randomly chosen, the attacker cannot select N' in a way such that  $u \pmod{N'} = 0$ .

#### 4.2 Mitigating Bypass Fault Attacks

To provide a more robust RSA authentication process against bypass attacks, we propose in Figure 5 the following scheme.

Let us make some comments on the above RSA signature authentication flow combating bypass attacks on e = 5.

- The function  $s_a := \mathsf{stamp}(\cdot)$  generates one word out of some (randomly) selected bits from a. The test  $s_a \neq s_a'$  checks that a has been changed during some previous modular multiplications steps, which implies that no loop bypass attack was launched.

- Protected branching ensures that an attacker introducing random faults needs to handle and manipulate multiple hard to fault-controllable computations simultaneously to be successful.

```

input: m, S, N

ROM (or fuse) storage: h_N, X, Y

1. /* validate N

a. choose random number r;

b. u := r \cdot N;

c. t := \mathsf{hash}(N);

d. if t \neq h_N then output "fail" and stop;

2. /* validate m with authentic N interleaved a. h_m := \mathsf{hash}(m);

b. a := (S + u) \pmod{N};

c. b := a^e \mod N;

d. extract the expected hash value e_m from b;

e. if h_m \neq e_m then output "fail" and stop;

"accept" message m if and only if N and m were valid

```

Fig. 4. RSA signature authentication flow combating Seifert-like attacks

```

input: m, S, N

ROM (or fuse) storage: h_N

generate secret 32-bit rnd number 0 < sec_{init} < 2^{32} - 4;

t := \mathsf{hash}(N);

h_m := \mathsf{hash}(m);

a := S:

s_a := \mathsf{stamp}(a); /* generate one word from some selected bits of a

repeat 2 times

a := a^2 \bmod N;

a := a \cdot S \mod N;

s'_a := \mathsf{stamp}(a);

extract the expected hash value e_m from a;

sec := sec_{init}

/* validate all steps with protected branch

if h_N = t \&\& sec++ \land e_m = h_m \&\& sec++ \land s_a \neq s'_a \&\& sec++ then

"accept" the signture iff (sec--)--=sec_{init}++

output "fail" and stop;

```

**Fig. 5.** RSA signature authentication flow combating bypass attacks on e=5

The delay of decision whether or not to accept the signature, to the end of the procedure, increases the random space of the program counter. This makes it more difficult to find an error that would generate the right bypass.

#### 4.3 Mitigating Permanent Fault — A Mission Impossible?

According to our above very strong attack through permanent fault attacks it is indeed very difficult to design some mitigation strategy against permanent faults. In order to do so, we have to make the following very strong assumption. It is physically possible to safely embed a symmetric key k into the device which cannot be read out (even by reverse-engineering methods) "too" easily. This key k can then be used to hide the exact N validation step from the attacker. Note that the attack is enabled because the attacker knows that the device compares  $\mathsf{hash}(N)$  to its expected value. To counter this attack, we propose to have the device use the key in order to check for a different expected value, namely  $h_{\mathsf{k}N} := \mathsf{hash}(\mathsf{k}||N)$ , which depends on both k and N. Note that  $h_{\mathsf{k}N}$  can be different from device to device (to resist the potential for BORE attacks). Figure 6 illustrates an authentication flow combating permanent fault attacks.

```

reverse-engineering protected embedded secret key k

ROM (or fuse) storage: h_{kN} /* h_{kN} := hash(k||N) input: m, S, N

1. /* validate N

a. t := \text{hash}(\textbf{k}||N);

b. if t \neq h_{kN} then output "fail" and stop;

2. /* validate m

a. h_m := \text{hash}(m);

b. a := S^e \mod N;

c. extract the expected hash value e_m from a;

d. if h_m \neq e_m then output "fail" and stop;

"accept" message m if and only if N and m were valid

```

**Fig. 6.** RSA signature authentication flow combating permanent fault attacks on N

### Acknowledgments

The authors would like to thank Eric Brier, Benoit Chevallier-Mames, Mathieu Ciet, and Christophe Clavier for sharing an early version of their paper [BCCC].

#### References

```

[And] R. Anderson, Security Engineering, John Wiley & Sons, Ltd., 2001.

[ABFHS] C. Aumüller, P. Bier, W. Fischer, P. Hofreiter, J.-P. Seifert, "Fault attacks on RSA: Concrete results and practical countermeasures", Proc. of CHES '02, Springer LNCS, pp. 261-276, 2002.

```

- [BGIR<sup>+</sup>] B. Barak, O. Goldreich, R. Impagliazzo, S. Rudich, A. Sahay, S. Vadhan, and K. Yang, "On the (Im)possibility of Obfuscating Programs", Crypto '01, pp. 1-18, 2001, LNCS vol. 2139, 2001.

- [BCNT<sup>+</sup>] H. Bar-El, H. Choukri, D. Naccache, M. Tunstall, C. Whelan, "The Sorcerer's Apprentice Guide to Fault Attacks", Proc. of IEEE 94(2):370-382, 2006.

- [BCCC] E. Brier, B. Chevallier-Mames, M. Ciet, and C. Clavier, "Why One Should Also Secure RSA Public Key Elements", Cryptographic Hardware and Embedded Systems CHES 2006, Lecture Notes in Computer Science, Springer-Verlag, 2006.

- [BMM] I. Biehl, B. Meyer, and V. Müller, "Differential fault analysis on elliptic curve cryptosystems", Advances in Cryptology CRYPTO 2000, vol. 1880 of LNCS, pp. 131146, Springer, 2000.

- [BOS] J. Blömer, M. Otto, J.-P. Seifert, "A new CRT-RSA algorithm secure against Bellcore attacks", Proc. of 10th ACM Conference on Computer and Communications Security, ACM Press, pp. 311-320, 2003.

- [BDL] D. Boneh, R. A. DeMillo, R. Lipton, "On the Importance of Eliminating Errors in Cryptographic Computations" Journal of Cryptology 14(2):101-120, 2001.

- [CJ] M. Ciet, M. Joye, "Elliptic curve cryptosystem in presence of permanent and transient faults", *Designs Codes and Cryptography* **36**(1), 2005.

- [FIB] FIB (Focused Ion Beam), http://www.ith.co.il/specs/fib.html.

- [Har] J.S. Harbour, The Black Art of Xbox Mods, Sams, 2004.

- [Hua] A. "Bunnie" Huang, Hacking the Xbox, No Starch Press, Inc., San Francisco, 2003.

- [LP] K. Lemke, C. Paar, "An Adversarial Model for Fault Analysis against Low-Cost Cryptographic Devices", Workshop on Fault Diagnosis and Tolerance in Cryptography - FDTC 2006, Lecture Notes in Computer Science, Springer-Verlag, 2006.

- [MvOV] A. J. Menezes, P. van Oorschot, S. Vanstone, Handbook of Applied Cryptography, CRC Press, New York, 1997.

- [Mui] J.A. Muir, "Seiferts RSA fault attack: Simplified analysis and generalizations", IACR Eprint archive 2005.

- [QS] J.-J. Quisquater, D. Samyde, "Eddy current for Magnetic Analysis with Active Sensor", Esmart 2002, Nice, France, September 2002.

- [Sei] J.-P. Seifert, "On authenticated computing and RSA-based authentication", Proc. of ACM Conference on Computer and Communications Security 2005, pp. 122127, 2005.

- [Unl] HU-Cards, Unlooper devices, http://www.hu-cards.org/products.html.

# Wagner's Attack on a Secure CRT-RSA Algorithm Reconsidered

Johannes Blömer<sup>1,⋆</sup> and Martin Otto<sup>2,⋆⋆</sup>

m.otto@siemens.com

Abstract. At CCS 2003, a new CRT-RSA algorithm was presented in [BOS03], which was claimed to be secure against fault attacks for various fault models. At CCS 2004, David Wagner presented an attack on the proposed scheme, claiming that the so-called BOS scheme was insecure for all presented fault models [Wag04]. However, the attack itself contains a flaw which shows that although the BOS scheme is broken in some fault models, it is not broken in the most realistic "random fault model". This paper points out the flaw in the attack on the BOS scheme, aiming to clarify this issue.

**Keywords:** CRT-RSA, fault attacks, smartcards, BOS-Scheme, Wagner's attack.

#### 1 Introduction

At CCS 2003, Blömer, Otto, and Seifert presented a new CRT-RSA algorithm, which was claimed to be secure against fault attacks [BOS03]. One year later, at CCS 2004, Wagner published an acclaimed attack on the so-called *BOS scheme* that he claimed to break the scheme [Wag04]. Wagner's results are correct for most of the fault models defined in [BOS03], namely models, where an adversary is assumed to be able to target individual bits and bytes in a selected variable.

However, the attack on the most often used fault model presented in [BOS03] contains a flaw, which renders the attack invalid against the BOS scheme. This flaw seems to be overlooked easily. Consequently, the attack is widely cited in various publications, e.g., [CJ05], [Gir05], without realizing the implications of the flaw.

In this paper, we point out the flaw in Wagner's attack in detail, aiming to clarify this issue. Moreover, we present the correct attacks and suggest possible countermeasures.

This paper is organized as follows. In Section 2, we briefly recall the fault models used in both papers, [BOS03] and [Wag04]. In Section 3, we recall the

<sup>&</sup>lt;sup>1</sup> Paderborn University, Institute for Computer Science, 33095 Paderborn, Germany bloemer@uni-paderborn.de

$<sup>^2</sup>$  Siemens AG, Corporate Technology CT IC3, Otto-Hahn-Ring 6, 81730 Munich, Germany

<sup>\*</sup> Research partially supported by a research grant of Intel Cop., Portland, USA.

<sup>\*\*</sup> This work was done during Ph.D. studies at the University of Paderborn, supported by the DFG graduate school No. 693 and the PaSCo Institute, Paderborn.

L. Breveglieri et al. (Eds.): FDTC 2006, LNCS 4236, pp. 13-23, 2006.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2006

original BOS scheme as proposed in [BOS03]. Section 4 is devoted to Wagner's attack and its analysis. Here, Section 4.1 describes the correct attacks and points out possible countermeasures. Section 4.2 analyzes the flawed attack on the BOS scheme in the "random fault model" and points of the erroneous part. Section 5 concludes the paper.

#### 2 Fault Models

In [BOS03], the following five fault models have been defined and used as a basis for the security claims. Note that we denote by l(X) the binary length of a variable X.

#### Fault Model #1: Precise Bit Errors

Parameter setting. For this strong fault model, we assume that the adversary has precise control on both timing and location. This means that the adversary knows the attacked bit as well as the attacked operation. Note that an attack usually happens before the variable is used in a line of an algorithm. We assume that only a single bit is affected. This resembles the "bit set or reset" (bsr) fault type that is achieved by attacks described in [SA02] or [QS02] on RAM or EEPROM of an unprotected smartcard.

Mathematical model. This attack can be modeled as an addition or subtraction of a single bit, i.e., a variable X is changed to  $X' = X \pm 2^k$  for  $0 \le k \le l(X) - 1$ .

Motivation from the real world. Although high-end smartcards implement sophisticated hardware countermeasures, many smartcards currently used are either too old or too cheap to do so. Hence, this fault model is a realistic one. It assumes the strongest adversary and the weakest card. Since algorithms secure in this fault model are secure in the weaker models as well, it is a particularly interesting model.

#### Fault Model #2: Precise Byte Errors

Parameter setting. In this scenario, we assume that the timing is precise. Hence, a specific operation can be targeted. However, control on location is loose, i.e. the number of bits affected can only be bounded by a block of few bits (we assume a byte). We allow any fault type in this model, e.g., stuck-at faults, bit flip faults, or random faults (cf. [Ott05]).

Mathematical model. The attack can be modeled as an addition or subtraction of an unknown error byte at a known position, i.e., a variable X is changed to  $X' = X \pm b \cdot 2^k$  for a  $known \ 0 \le k \le l(X) - 8$  and an unknown  $b \in \mathbb{Z}_{2^8}$ .

Motivation from the real world. This model is motivated by the fact that the strong adversary's power defined in Fault Model #1 is reduced on smartcards if encryption of the data is used. Usually, all data stored in EEPROM and RAM is encrypted [RE00]. Hence, if an error is induced into memory, the CPU will see a random block of data. The same model is derived if the bus lines are attacked.

#### Fault Model #3: Unknown Byte Errors

Parameter setting. In this scenario, we assume loose control on both timing and location. The loose control on location means that a certain variable can be targeted but the number of bits affected can only be bounded by a block of few bits (usually a byte). In addition, loose control on timing means that the attacker can only affect the variable within a specific time frame that usually contains several instructions. The exact instruction affected by the attack is unknown. Hence, the attacker does not know for sure which byte of the variable is currently used by the algorithm. Again, we allow any fault type in this model.

Mathematical model. This attack can be modeled as an addition or subtraction of an error byte, i.e., a variable X is changed to  $X' = X \pm b \cdot 2^k$  for an unknown  $0 \le k \le l(X) - 8$  and an unknown  $b \in \mathbb{Z}_{2^8}$ .

Motivation from the real world. This model is motivated by the fact that attacks on EEPROM and RAM with address scrambling (cf. [RE00]) will not allow to specify when the attacked block is requested by the CPU. Encryption of the memory ensures that a faulty bit affects a whole block of data.

#### Fault Model #3': Unknown Byte Errors in Unknown Variables

Parameter setting. This model assumes loose control on location, once again a whole byte is affected, and no control on timing. Due to the latter it is unknown at which exact time within the program the attack is mounted. It is even unknown, which variable is faulty.

Mathematical model. We model this type of fault as a variable dependent error, i.e., a variable X is changed to  $X' = X \pm b \cdot 2^k$  for an  $\operatorname{unknown} 0 \le k \le l(X) - 8$  and an unknown  $b \in \mathbb{Z}_{2^8}$ . Note that due to the unprecise timing, the attacked variable X is also unknown (to some degree).

Motivation from the real world. The strong adversary's power defined in Fault Model #1 is effectively reduced to this model if the smardcard uses memory encryption in RAM and EEPROM. This causes any bit fault to affect a whole block of data. In addition, some smartcards use a randomized clock (cf. [CCD00]). In this case, the attacker knows that a successful attack will change a block of data. But he does not know the exact time of the change within the algorithm. Therefore the attacker does not know the position of the block as it is used in the CPU.

#### Fault Model #4: Random Errors

Parameter setting. In this fault model, we assume that the adversary has no control on the location of a fault and only a loose timing, i.e., he can target an interval of some operations. This interval may have been derived from other sources of information, for example from the power profile of the card (see [ABF<sup>+</sup>02]). The number of affected bits is unknown.

Mathematical model. We model this uncertainty on the number of affected bits by a random fault. We assume that for a given variable X, the uniformly distributed

random value  $f(X) \in [0, 2^{l(X)} - 1]$  is used by the algorithm. In this model, any fault may result in any faulty value.

Motivation from the real world. This scenario is motivated by strong high-end smartcards completely armed with countermeasures. Memory encryption, address scrambling and a randomized clock imply that any error induced into memory or the CPU at a vague point will leave the attacker at most with the information that a certain variable is faulty. It therefore enforces a very weak adversary.

#### 3 The BOS Scheme

The BOS scheme as presented in [BOS03] extends an idea proposed by Shamir (see [Sha99]) and the idea of "infective computations" as introduced by Yen, Kim, Lim, and Moon in [YKLM01] and [YKLM03].

Infective computation means that any error introduced by a fault attack on the CRT-RSA algorithm propagates through the whole computation. In particular, if it can be ensured that in CRT-RSA a faulty signature will always be faulty modulo both prime factors, a Bellcore attack as presented in [BDL01] will be prevented.

The BOS scheme proposed in [BOS03] extends Shamir's idea to protect every single computation step of the signature algorithm, including the CRT combination. This is achieved by using two small integers  $t_1$  and  $t_2$  to compute  $S_p = m^d \mod pt_1$  and  $S_q = m^d \mod qt_2$ . These values are combined to  $S \mod Nt_1t_2$  via the CRT. This combination with a larger modulus allows to use infective computation steps afterwards. These infective steps ensure that an error will cause the final signature to be false modulo both primes p and q. Infective computations not only avoid single points of failures. They also allow a device to continue its computation, even if a fault is detected.

```

Algorithm 1: Infective CRT-RSA

```

```

\begin{array}{c} \textbf{Input:} \  \, \mathsf{A} \  \, \mathsf{message} \  \, \mathsf{m} \in \mathbb{Z}_{\mathsf{N}} \\ \textbf{Output:} \  \, \mathsf{Sig} := \mathsf{m}^d \  \, \mathsf{mod} \  \, \mathsf{N} \  \, \mathsf{or} \  \, \mathsf{a} \  \, \mathsf{random} \  \, \mathsf{number} \  \, \mathsf{in} \  \, \mathbb{Z}_{\mathsf{N}} \\ \textbf{In} \  \, \mathbf{Memory:} \  \, \mathsf{p} \cdot \mathsf{t}_1, \mathsf{q} \cdot \mathsf{t}_2, \mathsf{N}, \mathsf{N} \cdot \mathsf{t}_1 \cdot \mathsf{t}_2, \mathsf{d}_{\mathsf{p}}, \mathsf{d}_{\mathsf{q}}, \mathsf{t}_1, \mathsf{t}_2, \mathsf{e}_{\mathsf{t}_1}, \  \, \mathsf{and} \  \, \mathsf{e}_{\mathsf{t}_2} \\ 1 \  \, \mathsf{Let} \  \, \mathsf{S}_{\mathsf{p}} := \mathsf{m}^{\mathsf{d}_{\mathsf{p}}} \  \, \mathsf{mod} \  \, \mathsf{p} \cdot \mathsf{t}_1 \\ 2 \  \, \mathsf{Let} \  \, \mathsf{S}_{\mathsf{q}} := \mathsf{m}^{\mathsf{d}_{\mathsf{q}}} \  \, \mathsf{mod} \  \, \mathsf{q} \cdot \mathsf{t}_2 \\ 3 \  \, \mathsf{Let} \  \, \mathsf{S} := \mathsf{CRT}(\mathsf{S}_{\mathsf{p}}, \mathsf{S}_{\mathsf{q}}) \  \, \mathsf{mod} \  \, \mathsf{N} \cdot \mathsf{t}_1 \cdot \mathsf{t}_2 \\ 4 \  \, \mathsf{Let} \  \, \mathsf{c}_1 := (\mathsf{m} - \mathsf{S}^{\mathsf{e}_{\mathsf{t}_1}} + 1) \  \, \mathsf{mod} \  \, \mathsf{t}_1 \\ 5 \  \, \mathsf{Let} \  \, \mathsf{c}_2 := (\mathsf{m} - \mathsf{S}^{\mathsf{e}_{\mathsf{t}_2}} + 1) \  \, \mathsf{mod} \  \, \mathsf{t}_2 \\ 6 \  \, \mathsf{Let} \  \, \mathsf{Sig} := \mathsf{S}^{\mathsf{c}_1 \cdot \mathsf{c}_2} \  \, \mathsf{mod} \  \, \mathsf{N} \\ 7 \  \, \mathsf{Output} \  \, \mathsf{Sig} \end{array}

```

Selecting the Parameters. As a precomputation step that can be performed for any smartcard at production time, generate a valid RSA key with (N, e),  $N = p \cdot q$ , as the public key and d as the corresponding private key satisfying  $e \cdot d \equiv 1 \mod \varphi(N)$ .

Additionally, select two integers  $t_1$  and  $t_2$  of sufficiently large bitlength to withstand exhaustive search (recommended to comprise of at least 60 - 80 bits) which must satisfy several conditions in order to allow a secure scheme:

```

1. t_1 and t_2 must be coprime

2. \gcd(d, \varphi(t_1)) = 1 and \gcd(d, \varphi(t_2)) = 1

3. t_1 and t_2 are squarefree

4. t_i \equiv 3 \mod 4 for i \in \{1, 2\}

5. t_2 \not\mid X = pt_1 \cdot ((pt_1)^{-1} \mod qt_2)

```

Let  $d_p := d \mod \varphi(p \cdot t_1)$ ,  $d_q := d \mod \varphi(q \cdot t_2)$ . Afterwards, compute two corresponding public keys  $e_{t_1}$  and  $e_{t_2}$  such that  $d \cdot e_{t_i} = 1 \mod \varphi(t_i)$ . Store  $p \cdot t_1$ ,  $q \cdot t_2$ , N,  $N \cdot t_1 \cdot t_2$ ,  $d_p$ ,  $d_q$ ,  $t_1$ ,  $t_2$ ,  $e_{t_1}$  and  $e_{t_2}$  on the smartcard. It is easy to see that the algorithm computes the correct signature if no error occurs. In this case, the two infective variables  $c_1$  and  $c_2$  computed in Lines 4 and 5 are both equal to 1, hence,  $\operatorname{Sig} \equiv S \equiv m^d \mod N$ .

For details on the choice of the two primes, we refer to [BOS03] or [Ott05]. There, it is recommended to choose both  $t_i$  as strong primes.

#### 3.1 Obvious Security Considerations

Disclosure of most intermediate variables can be used to break the system. Attacks on most intermediate variables, e.g.,  $d_p$  or m, have a negligible success probability for almost all messages. However, there are messages, where an adversary can mount a successful Bellcore-like attack (as presented in [BDL01]) with extremely high probability. These messages depend on  $t_1$  or  $t_2$ , e.g.,  $m \equiv \pm 1 \mod t_1$  for an attack targeting  $d_p$ , or  $m \equiv 0 \mod t_1$  for an attack targeting m or the intermediate values of the exponentiation. Therefore, it is crucial to the security of Algorithm 1 that no intermediate variables are disclosed. This does not only hold for the secret randomization parameters  $t_1$  and  $t_2$ . As an example, assume that our countermeasure prevents a Bellcore attack on a faulty  $S_p$  using  $c_1 \neq 1$  and  $c_2 = 1$ . If  $c_1$  is revealed, we have

$$\gcd(m^{c_1} - Sig^e, N) = p.$$

# 4 Wagner's Attacks Against the BOS Scheme

In [BOS03], it is claimed that the proposed countermeasure secures the CRT-RSA algorithm against faults based on the Random Fault Model #4. Unfortunately, it does not provide sufficient security against faults based on the stronger fault models, namely the Single Bit Fault Model #1 or the Byte Fault Models #2 and #3. This has been described in detail by Wagner in [Wag04]. Moreover, another attack has been described in [Wag04]. However, the latter contains a flaw that seems to be overlooked easily. Consequently, the attack is widely cited without honoring the implications of the flaw. We describe the correct attacks and the flawed attack in detail.

In the following, we denote by  $\tilde{X}$  a faulty variable X and by e(X) the absolute error induced into X as an additive term, i.e.,  $\tilde{X} = X + e(X)$ . The possible values and distribution of the random variable e(X) depend on the chosen fault model.

#### 4.1 Bit and Byte Faults

For the BOS scheme, it has been described in Section 3.1 that if  $c_1 \neq 1$  or  $c_2 \neq 1$  and the infective value  $c_i$  is disclosed, an attacker can mount a Bellcore-like attack by computing  $\gcd(m^{c_i} - Sig^e, N)$ . This yields a factor of N. For bit faults and byte faults, the number of possible errors is rather small, hence, an adversary can guess a possible error value e(X), resulting from a fault induced into some variable X and try to verify his assumption.

As a concrete example, consider a transient fault induced into m according to the Single Bit Fault Model #1 in Line 1 of Algorithm 1. In this case,  $S_p$  is faulty and  $S_q$  is correct, hence, the variable S is faulty. As usual, we denote a faulty S by  $\tilde{S}$ . Since  $\tilde{S} \equiv S \mod qt_2$ , we have  $c_2 = 1$ . However, a faulty  $\tilde{m} = m + e(m)$  yields the value  $\tilde{S}_p = \tilde{m}^{d_p} \mod pt_1$ , hence, we have  $c_1 = (m - \tilde{m} + 1) \mod t_1 = 1 - e(m) \mod t_1$ . This is not equal to  $1 \mod t_1$ , since  $t_1 \not\mid e(m) = \pm 2^k$  for any choice of k > 0.

Let  $-t_1+1 < e(m) < 0$ . In this case, the modular reduction in the computation of  $c_1 = 1 - e(m) \mod t_1$  does not take place. For bit faults, all values of  $e(m) = -2^k$  for  $0 \le k \le l(t_1) - 1$  satisfy this condition, and for byte faults, all values of  $e(m) = b \cdot 2^k$  for  $-2^8 + 1 \le b \le -1$  and  $0 \le k \le l(t_1) - 8$ . In these cases,  $c_1$  can be recovered by testing all possible values for e(m) according to the chosen fault model. The probability of inducing such a usable fault is approximately  $1/2 \cdot l(t_1)/l(N)$  according to [Wag04], assuming a variant of the Byte Fault Models #2 and #3. The crucial fact exploited by this attack is that the set of usable errors is efficiently sampleable and highly probable, since they form a large fraction of all possible error values. Hence, an adversary can perform computations for all possible guesses in polynomial time and he can hope to induce a usable error after polynomial many tries. This is fundamentally different from random faults, where the number of possible faults is too large to be sampled in polynomial time.

Infective computations aim at randomizing the output, but they do not use an own source of randomness. Instead, they use the random source provided by the error. Consequently, their effectiveness depends on the quality of the random error source. If the error is truly random, i.e., uniformly distributed in a large set, a randomization of the final output is possible. Hence, an adversary using the Random Fault Model #4 faces a randomized faulty output, where the infective randomization strategy provides a good randomization. For all other attacks, which assume errors, that do not represent a good source of randomness, infective computations will always be insecure. This is what happens for the Bit Fault Model #1 and the Byte Fault Models #2 and #3, where most of the values  $e(m) \in \mathbb{Z}_{pt_1}$  occur with probability 0 and only a small fraction occurs with non-zero probability. Any distribution of the error, which is strongly biased or asymmetric, can be susceptible to the attack described above.

Simple Solution for Attacks with Efficiently Sampleable Errors. A simple solution to this problem is straightforward. If the adversary can always recover  $\tilde{S}$  if a strong fault model is used, the algorithm must not output a result. Hence, we present with Algorithm 2 a simple countermeasure suitable for bit and byte faults.

#### Algorithm 2: Secure CRT-RSA Algorithm with Explicit Checking Procedures

```

\begin{array}{l} \textbf{Input:} \  \, \mathsf{A} \  \, \mathsf{message} \  \, \mathsf{m} \in \mathbb{Z}_{\mathsf{N}} \\ \textbf{Output:} \  \, \mathsf{Sig} := \mathsf{m}^{\mathsf{d}} \  \, \mathsf{mod} \  \, \mathsf{N} \  \, \mathsf{or} \  \, \mathsf{a} \  \, \mathsf{random} \  \, \mathsf{number} \  \, \mathsf{in} \  \, \mathbb{Z}_{\mathsf{N}} \\ \textbf{In Memory:} \  \, \mathsf{p} \cdot \mathsf{t}_1, \mathsf{q} \cdot \mathsf{t}_2, \mathsf{N}, \mathsf{N} \cdot \mathsf{t}_1 \cdot \mathsf{t}_2, \mathsf{d}_{\mathsf{p}}, \mathsf{d}_{\mathsf{q}}, \mathsf{t}_1, \mathsf{t}_2, \mathsf{e}_{\mathsf{t}_1}, \  \, \mathsf{and} \  \, \mathsf{e}_{\mathsf{t}_2} \\ 1 \  \, \mathsf{Let} \  \, \mathsf{S}_{\mathsf{p}} := \mathsf{m}^{\mathsf{d}_{\mathsf{p}}} \  \, \mathsf{mod} \  \, \mathsf{p} \cdot \mathsf{t}_1 \\ 2 \  \, \mathsf{Let} \  \, \mathsf{S}_{\mathsf{q}} := \mathsf{m}^{\mathsf{d}_{\mathsf{q}}} \  \, \mathsf{mod} \  \, \mathsf{q} \cdot \mathsf{t}_2 \\ 3 \  \, \mathsf{Let} \  \, \mathsf{S} := \mathsf{CRT}(\mathsf{S}_{\mathsf{p}}, \mathsf{S}_{\mathsf{q}}) \  \, \mathsf{mod} \  \, \mathsf{N} \cdot \mathsf{t}_1 \cdot \mathsf{t}_2 \\ 4 \  \, \mathsf{Let} \  \, \mathsf{c}_1 := (\mathsf{m} - \mathsf{S}^{\mathsf{e}_{\mathsf{t}_1}} + 1) \  \, \mathsf{mod} \  \, \mathsf{t}_1 \\ 5 \  \, \mathsf{Let} \  \, \mathsf{c}_2 := (\mathsf{m} - \mathsf{S}^{\mathsf{e}_{\mathsf{t}_2}} + 1) \  \, \mathsf{mod} \  \, \mathsf{t}_2 \\ 6 \  \, \mathsf{lf} \  \, (\mathsf{c}_1 \neq 1) \  \, \mathsf{or} \  \, (\mathsf{c}_2 \neq 1) \  \, \mathsf{then} \  \, \mathsf{output} \  \, \mathsf{FAILURE} \\ 7 \  \, \mathsf{Output} \  \, \mathsf{S} \  \, \mathsf{mod} \  \, \mathsf{N} \\ \end{array}

```

Infective computations have the advantage to replace explicit checking procedures, which always pose a single point of failure. However, a weak source of randomness suggests to dispose of infective computations and return to the explicit checks. Explicit checking procedures are dangerous only if an adversary can induce two faults during one run of the algorithm. Moreover, modern high-end smartcards are equipped with a variety of countermeasures, which allow users to be confident that the strong power of an adversary is reduced to the Random Fault Model #4. Algorithm 1 is secure in this model.

More Sophisticated Solutions for Attacks with Efficiently Sampleable Errors. However, with a little additional work, it might also be possible to protect Algorithm 1 against bit or byte faults while still using infective computations. This is a new direction of research, hence, we will only briefly sketch the ideas here. Since the error does not provide enough randomness to sufficiently randomize the two infective values  $c_1$  and  $c_2$ , the algorithm needs to acquire another source of randomness. To show how this can add security, assume that we have two random values  $R_1$  and  $R_2$ .

The attack described above, using the Single Bit Fault Model #1 or the Byte Fault Models #2 and #2 to break Algorithm 1, exploits the fact that it can enumerate all possible values of the term  $S^{e_{t_1}}$  mod  $t_1$  efficiently, if m has been attacked in Line 1. If  $c_1$  is smaller than  $t_1$ , a reduction does not take place. The latter allows the adversary to recover  $c_1$  by testing all possible error values as described above, since the chance to induce such errors is very high. The same considerations apply for a fault induced into m in Line 2, however, due to symmetry, we will only describe attacks targeting the first line.

If the resulting value  $c_1 > 1$  is randomized by a sufficiently large random integer  $R_1$ , the value  $c_1$  will be a random value as well. In this case, the advantage of

the strong fault models #1, #2, and #3, which provide an efficiently sampleable set of error values, can no longer be used. We present the modified algorithm as Algorithm 3.

It is obvious from Algorithm 3, that  $c_1=c_2=1$  if no error occurs. In this case, we have  $m-S^{e_{t_i}}\equiv 0 \bmod t_i$  for  $i\in\{1,2\}$ . If both  $R_1$  and  $R_2$  are random integers with  $l(t_1)=l(t_2)$  bits, then there are  $2^{(l(t_1)-1)}$  many possible values for  $R_1$  and  $R_2$ . Consequently, there are  $2^{(l(t_1)-1)}$  many values for  $c_1$  and  $c_2$  unless  $m-S^{e_{t_i}}\equiv 0 \bmod t$ . Hence, the values  $c_1$  and  $c_2$  are random integers in  $\mathbb{Z}_{t_i}$  as well. Therefore, they cannot be recovered using only information about the induced error. In this case,  $c_1$  and  $c_2$  will not be disclosed unless an adversary has some knowledge about  $R_1$  and  $R_2$ . Therefore, the attack described in [Wag04] cannot be applied any longer.

#### Algorithm 3: Secure CRT-RSA Algorithm with Additional Randomization

However, randomness is expensive on smartcards. Hence, it is preferable to protect the CRT-RSA algorithm without requiring random values  $R_1$  and  $R_2$ , generated freshly for each run of the algorithm. Consequently, a new idea is to replace the notion of randomness by the notion of unpredictability. The attack described above requires than an adversary is able to enumerate all possible values for  $c_1$ . However, if the two factors  $R_1$  and  $R_2$  are large unknown values, the adversary loses the information about the set of possible values for faulty  $c_1$  and  $c_2$ . This might already be enough to defend against the attack described above. In this case, there are several possible choices for  $R_1$  and  $R_2$ , e.g.,

- two different fixed random values computed and stored on the card at production time,

- $-R_1 = R_2 = d,$

- $-R_1=R_2=S,$

- $-R_1 = p$ ,  $R_2 = q$  (or any combination of p and q),

- $-R_1 = S_p$ ,  $R_2 = S_q$  (or any combination of  $S_p$  and  $S_q$ ), or

- $-R_1 = H(r_1), R_2 = H(r_2)$ , where H is a cryptographically strong hash function and  $r_1$  and  $r_2$  are any of the values  $d, S, S_p$ , or  $S_q$ .

Since the adversary has no better choice to recover  $c_1$  and  $c_2$  than to check all possible values from  $\mathbb{Z}_{t_1}$  or  $\mathbb{Z}_{t_2}$  (depending on which line has been attacked),

it should be sufficient to choose  $R_1 = R_2$ . Of the above suggested choices for  $R_1$  and  $R_2$ , it is preferable to have  $R_1$  and  $R_2$  depend on S,  $S_p$ , and/or  $S_q$  rather than on other values, because these ensure that the random factors depend on the chosen message and on the induced fault, for a lot of possible fault locations. However, the security of Algorithm 3 has not yet been proven, it is still an open problem.

#### 4.2 Wagner's Attack

Another attack has been described in [Wag04] using a fault model close to Fault Model #4. If this attack was successful, it would render the use of Algorithm 1 useless as a countermeasure. The fault model proposed in [Wag04] uses an extremely asymmetric error distribution, where all faults only affect the lower l(x) - 160 bits of an affected variable x, whereas the highest 160 bits are unchanged. Therefore, it is somewhere between the Byte Fault Models #2 and #3 and the Random Fault Model #4. We will refer to this fault model as Wagner's Fault Model.

We consider Wagner's Fault Model to be leaving the defined models of BOS. It has never been considered before, and though it can be realized in practice, its practicability has not been demonstrated yet. Moreover, it cannot be achieved using the Random Fault Model #4, since an adversary can only hope to induce a random fault with an effect of the required kind with probability  $1/2^{160}$ , which is negligible. For bit faults and byte faults, however, this is possible with high probability. Moreover, if a smartcard only uses block-wise encryption of the data in memory, an attack can easily target the l(x) - 160 least significant bits of a variable x. Modern smartcards, however, implement a variety of countermeasures, which allows to put great confidence in the assumption that Wagner's Fault Model is unrealistic. Moreover, Wagner's attack requires several faulty results.

In the attack described in [Wag04], the modulus N in Line 6 of Algorithm 1 is targeted with Wagner's Fault Model. This attack aims at disclosing  $t_1$  and  $t_2$ . Such a disclosure allows to break the system as explained in Section 3.1. A correct "large" signature S as computed in Line 3 can be written as  $S = (S \mod N) + k \cdot N$ , for some  $0 \le k < 2^{161}$  (since  $l(t_1 \cdot t_2) \le 2^{160}$ ). A fault induced into N according to this new fault model yields the faulty value  $\tilde{N}$ . Given the correct result  $Sig = S \mod N$  and a faulty final result  $\widetilde{Sig} = S \mod \tilde{N}$ , we have

$$\widetilde{Sig} - Sig \equiv S - Sig \equiv S - S + k \cdot N \equiv k \cdot (N - \tilde{N}) \bmod \tilde{N}.$$

Since we know that  $|\tilde{N}-N| \leq 2^{l(N)-161}$ , we have  $|k\cdot(\tilde{N}-N)| < 2^{l(N)}$ . With probability at least 1/2, we have  $l(N) = l(\tilde{N})$ , hence, when computing  $\widetilde{Sig} - Sig \mod \tilde{N}$ , there will be no overflow or modular reduction with sufficiently high probability. In this case, an integer multiple of k is known to the adversary and several attacks on N will allow him to compute k. This can be done by computing many pair-wise gcd's and taking the majority vote. Once an adversary has k, he can compute  $S = Sig + k \cdot N$ . Wagner erroneously assumes that  $t_1 \cdot t_2 = (S - Sig)/N$ .

A closer analysis shows the flaw. Let  $t = t_1 \cdot t_2$ ,  $S_t = S \mod t$ , and  $S_N = S \mod N$ . This means that we have  $S = S_N + k \cdot N$ , and  $Sig = S_N$ . Consequently, the term (S - Sig)/N = k yields  $k \equiv (S_t - S_N)N^{-1} \mod t$  (Garner's formula). If t ist fixed, then  $N^{-1} \mod t$  is also fixed. However, due to the term  $S_t$ , the value of  $k = (S_t - S_N)N^{-1} \mod t$  can take on any value in  $\mathbb{Z}_t$ . Moreover, since t and d are unknown, given a message m it should be hard for an attacker to predict the value  $S_t$ . Therefore, what the attacker will most probably see if he determines the value k for messages m are random looking elements in  $\mathbb{Z}_t$ . To determine t from this kind of information is not feasible. Hence, we consider this attack not to be a threat to our proposed algorithm.

#### 5 Conclusion

We have shown that Wagner's attack on the BOS scheme does not completely break the security of the BOS scheme due to a flaw in the proof. Therefore, the BOS scheme should still be considered secure against fault attacks in the Random Fault Model.

#### References

- [ABF<sup>+</sup>02] C. Aumüller, P. Bier, W. Fischer, P. Hofreiter, and J.-P. Seifert, Fault attacks on RSA with CRT: Concrete results and practical countermeasures, Workshop on Cryptographic Hardware and Embedded Systems 2002 (CHES 2002) (Hotel Sofitel, San Francisco Bay (Redwood City), USA), August 13–15 2002.

- [BDL01] D. Boneh, R. A. DeMillo, and R. J. Lipton, On the importance of eliminating errors in cryptographic computations, J. Cryptology 14 (2001), no. 2, 101–119.

- [BOS03] J. Blömer, M. Otto, and J.-P. Seifert, A new CRT-RSA algorithm secure against Bellcore attacks, Conference on Computer and Communications Security — CCS 2003 (V. Atluri and P. Liu, eds.), ACM SIGSAC, ACM Press, 2003, pp. 311–320.

- [CCD00] C. Clavier, J.-S. Coron, and N. Dabbous, Differential power analysis in the presence of hardware countermeasures, Cryptographic Hardware and Embedded Systems – Proceedings of CHES 2000, Worcester, MA, USA, Lecture Notes in Computer Science, vol. 1965, Springer-Verlag, 2000, pp. 252– 263.

- [CJ05] M. Ciet and M. Joye, Practical fault countermeasures for chinese remaindering based RSA, 2nd Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC 05) (Edinburgh, Scotland), September 2, 2005.

- [Gir05] C. Giraud, Fault resistant RSA implementation, Fault Diagnosis and Tolerance in Cryptography FDTC 2005 (Edinburgh, Scotland) (L. Breveglieri and I. Koren, eds.), September 2, 2005.

- [Ott05] M. Otto, Fault attacks and countermeasures, Ph.D. thesis, University of Paderborn, 2005, http://www.s.uni-paderborn.de/cs/ag-bloemer/forschung/publikationen/DissertationMartinOtto.pdf.